Arduino Sketch Sound Demo

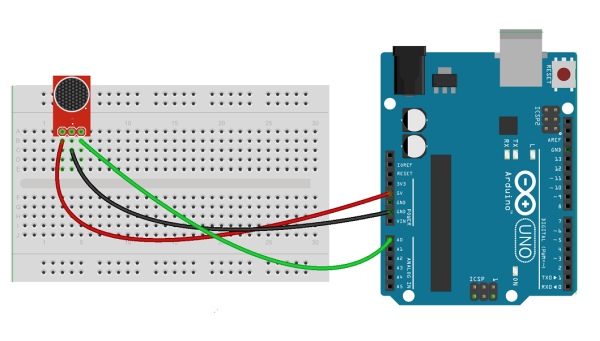

This sketch is used by Exercise: Multichannel Bipolar Transistor Driver. Full Source Code The full code is all in one file SoundDemo.ino. // SoundDemo – generate sound using a speaker and pager motor // // Copyright (c) 2016, Garth Zeglin. All rights reserved. Licensed under the // terms of the BSD 3-clause license as included in LICENSE. […]