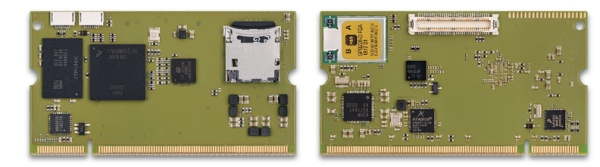

CPU Module with processor from the i.MX8 series

The new Trizeps VIII uses the i.MX 8M processor from the NXP i.MX8 series. The CPU Module provides the high performance demands of current video, voice, and audio processing, either for industrial or home automation, streaming audio applications, or for modern imaging devices.

Available with Linux and Android operating systems, Windows 10 IoT Core is announced.

- NXPTM i.MX 8M ARM® Quad-/Dual-Core Cortex A53 CPU up to 1.5 GHz, additional Cortex M4

- Configurable FPGA, e.g. with MIPI to RGB converter

- Additional NXPTM Kinetis V ARM® Cortex M0+ MCU with e.g. CAN, ADC, SPI, I2C interfaces

- Up to 4 GByte LPDDR4-3200 RAM, 32Bit

- 1 GBit Ethernet, USB 3.0

- Onboard WLAN/Bluetooth module (optional)

- LVDS (Single or Dual) Transceiver

- Trizeps SODIMM-200 compatible, compact and scalable

Features:

1 NXP i.MX 8M Arm Cortex A53 CPU up to 1.5 GHz (Quad-, Dual-Core), additional Cortex M4 – 2 LPDDR4-3200 RAM (32 Bit, up to 4 GByte) – 3 SODIMM 200 Connector, Interfaces: UART (4x), SPI, SDIO, QSPI, I2C (3x), GPIO, PWM, USB 3.0 (2x), Headphone (stereo), Line-In (stereo), Microphone, Speaker, SPDIF In/Out, Serial Multichannel Audio, PCM, PCIe, FPGA configurable pins (e.g. display RGB16/18/24, SPI/UART/GPIO, parallel camera), Kinetis MCU Pins (e.g. CAN, ADC 16 bit, UART, SPI), Ethernet (1 Gbit, 100/10 Mbit), +3V3 power supply – 4 Socket for µSD cards (4 Bit, lockable, optional) or eMMC (8 Bit, Standard) – 5 WLAN and Bluetooth UFL Coax connector (2,4 GHz, 5 GHz) – 6 WLAN UFL Coax connector (2,4 GHz, 5GHz) – 7 WLAN-Bluetooth Module (optional): 802.11 a/b/g/n/ac 2×2 MU-MIMO / Bluetooth 4.2, 5.0 – 8 Power Management IC (PMIC) – 9 Single or Dual LVDS Transceiver – 10 1 Gbit Ethernet Phy – 11 NXP Kinetis MCU, Cortex M0+ – 12 High-Speed board-to-board connector, Interfaces: HDMI, Mipi DSI (4 channel), Single or Dual LVDS, 2x Mipi CSI (4 channel), Ethernet SIOP – 13 HiFi Audio Codec – 14 FPGA up to 4300 LUTs – 15 JTAG (i.MX 8M CPU) – 16 JTAG (FPGA and MCU)

Constantly high quality through multi-stage test of each individual CPU module

To ensure a constantly high quality, each individual CPU module is passed through a multi-stage test. The test result covers 100% of all interfaces.

- AOI/MOI: Multiple automatic and manual optical control of each CPU module during the production.

- JTAG/Boundary Scan Test: JTAG/Boundary Scan Test: The signal of each pin which is accessible via the JTAG chain is checked for connection, shorts, missing pull-up/down resistors. The DDR Ram is tested for row/column pin assignment.

- Functional tests of high-speed and analog interfaces (Ethernet, display, USB, audio, etc.) which are not testable via JTAG

SODIMM Standard

The Trizeps VIII includes the Keith & Koep SODIMM 200 Standard, the world‘s longest existing SODIMM standard. Like no other module standard, the SODIMM 200 ensures the pin compatibility of the Trizeps modules. The main difference of the Trizeps VIII Mini is the missing address/data bus, which is no longer supported by the i.MX 8M CPU. The pins, which are no longer needed for this function, are used for GBit Ethernet and USB 3.0 signals. Trizeps VIII and Trizeps VIII Mini are mostly pin compatible.

Read more: SODIMM-STYLE MODULES EXPAND UPON I.MX8M AND I.MX8M MINI