An industry’s first, the 12-layer 3D-TSV (Through Silicon Via) technology developed by Samsung Electronics enables the stacking of 12 DRAM chips using more than 60,000 TSV holes, while maintaining the same thickness as current 8-layer chips. By Julien Happich @ eenewseurope.com

Developed for the mass production of high-performance chips, the layered packaging technology requires pinpoint accuracy to vertically interconnect the DRAM chips through a three-dimensional configuration of TSV holes. The thickness of the package (720㎛) remains the same as current 8-layer High Bandwidth Memory-2 (HBM2) products, which is a substantial advancement in component design. This will help customers release next-generation, high-capacity products with higher performance capacity without having to change their system configuration designs.

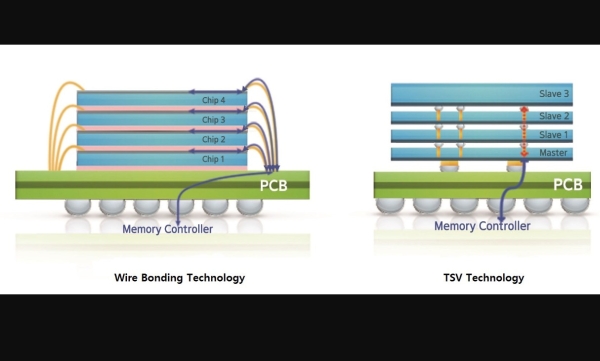

In addition, the 3D packaging technology also features a shorter data transmission time between chips than the currently existing wire bonding technology, resulting in significantly faster speed and lower power consumption. “Packaging technology that secures all of the intricacies of ultra-performance memory is becoming tremendously important, with the wide variety of new-age applications, such as artificial intelligence (AI) and High Power Computing (HPC),” said Hong-Joo Baek, executive vice president of TSP (Test & System Package) at Samsung Electronics.

As Moore’s law scaling reaches its limit, the role of 3D-TSV technology is expected to become even more critical. We want to be at the forefront of this state-of-the-art chip packaging technology.

Read more: SAMSUNG UNVEILS 12-LAYER 3D-TSV CHIP PACKAGING TECHNOLOGY