New: Introducing the BeagleLogic cape. Click here for more details

Click Here for instructions on how to build BeagleLogic kernel modules

Click Here to get started, once the modules have been built and installed

Your BeagleBone. Now a Logic Analyzer.

BeagleLogic turns your BeagleBone [Black] into a 14-channel, 100Msps Logic Analyzer. Once loaded, it presents itself as a character device node /dev/beaglelogic.

The core of the logic analyzer is the ‘beaglelogic’ kernel module that reserves memory for and drives the two Programmable Real-Time Units (PRU) via the remoteproc interface wherein the PRU directly writes logic samples to the System Memory (DDR RAM) at the configured sample rate one-shot or continuously without intervention from the ARM core.

BeagleLogic can be used stand-alone for doing binary captures without any special client software.

dd if=/dev/beaglelogic of=mydump bs=1M count=1

is sufficient to grab a binary dump, once sample rate has been configured via sysfs.

When used in conjunction with the sigrok library, BeagleLogic supports software triggers and decoding over 30 different digital protocols. Since the BeagleLogic bindings for libsigrok have been merged upstream, the latest built-from-source sigrok libraries and tools support capturing from BeagleLogic.

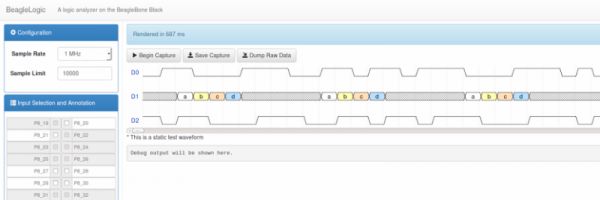

BeagleLogic also offers a web interface (demo) which, once installed on the BeagleBone, can be accessed from port 4000 and can be used for low-volume captures (upto 3K samples). It makes BeagleLogic a useful tool for beginners as a learning tool to learn about digital protocols.

Core Specifications:

- Sample Rate: 10 Hz to 100 MHz [(100/N) MHz; integer N]

- Sample Size: 8-bit or 16-bit [a maximum of 14 inputs: P8_39 to P8_46, P8_27 to P8_30, P8_20 and P8_21 (after disabling the eMMC)]

For more detail: BeagleLogic – BeagleBone Logic Analyzer