3D TLC NAND flash based products are already dominating in SSD for consumers. Sophisticated NAND FLASH manufacturing technology, new advanced FLASH controllers and firmware now allow using 3D TLC NAND in industrial grade SSDs.

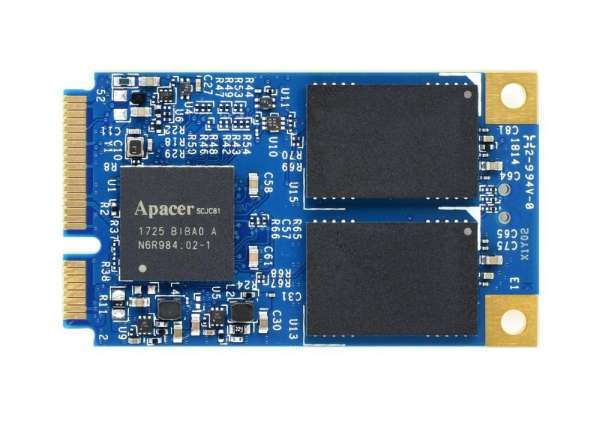

Apacer introduces a new ST170 series in 2.5″ SSD, M.2, mSATA, MO-297, CFast and uSSD form factors.

To make products reliable and simultaneously provide high performance, they use:

- Error Correction/Detection

- Power Failure Management

- Flash memory Bad-Block Management

- Global wear levelling – all spare blocks in all flash chips in the product are managed together in a single pool. Controller tries to distribute the writes evenly to all flash memory blocks. You can judge the efficiency of algorithm from SMART attributes Max. erase count and Avg. erase count.

- End-to-end data protection – a feature that extends error control to cover the entire path from the host computer to the drive and back, and ensures data integrity at multiple points in the path to enable reliable delivery of data transfers

- SMART (Self-Monitoring, Analysis and Reporting Technology)

- Thermal sensor – regularly check SMART attribute Temperature and decrease SSD workload to avoid rising SSD temperature above 70°C

- Page-level flash translation layer

- Hyper cache technology – portion of the available capacity is used as SLC (1bit-per-cell) NAND flash. Only two values are written (0, 1) instead of eight.

- Over-provisioning – certain portion of the SSD capacity is reserved exclusively for increasing garbage collection (GC) efficiency, especially when the SSD is filled to full capacity or it is under heavy mixed (sequential-random) workload.

- TRIM support – the command enables the operating system to inform the SSD flash controller of blocks that contain unnecessary data, typically data that the operating system has deleted. The controller then erases the unnecessary blocks and releases them for use.

Error Correction/Detection

When application writes data to SSD, flash controller writes the data, firmware information and ECC (error correction code) to flash memory. Controller writes 40-bit BCH (Bose-Chaudhuri-Hocquengham) ECC per 1KB of data for SSD from SM210-25 series, for example. When controller reads the data from flash memory, it uses ECC to check the data validity and correct errors.

Read more: 3D TLC NAND Flash technology enters the Industry