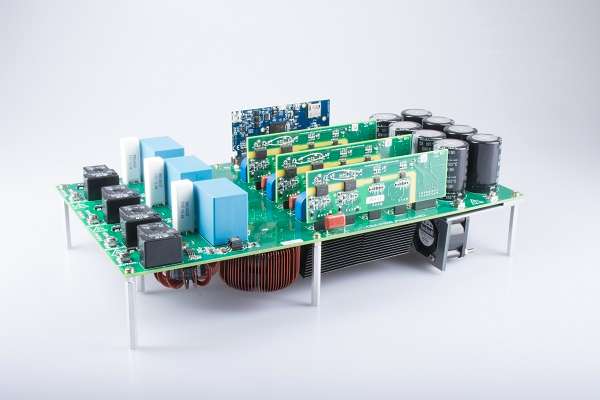

This verified reference design provides an overview of how to implement a three-level three-phase SiC-based DC: AC grid-tie inverter stage. The higher switching frequency of 50KHz reduces the size of magnetics for the filter design and enables higher power density.

This verified reference design provides an overview on how to implement a three-level three-phase SiC based DC:AC grid-tie inverter stage. The higher switching frequency of 50KHz reduces the size of magnetics for the filter design and enables higher power density. The use of SiC MOSFETs with switching loss ensures higher DC bus voltages of up to 1000V and lower switching losses with a peak efficiency of 99 percent. This design is configurable to work as a two-level or three-level inverter.The system is controlled by a single C2000 microcontroller (MCU), TMS320F28379D, which generates PWM waveforms for all power electronic switching devices under all operating modes.

This design is configurable to work as a two-level or three-level inverter. The system is controlled by a single C2000 microcontroller (MCU), TMS320F28379D, which generates PWM waveforms for all power electronic switching devices under all operating modes.

Features

- Rated nominal/max input voltage at 800V/1,000VDC

- Max 10kW/10KVA output power at 400VAC 50/60Hz grid-tie connection

- Operating power factor range from 0.7lag to 0.7lead

- High voltage (1,200V) SiCMosFET based full bridge inverter for peak efficiency of 99%

- Less than 2% output current THD at full load

- Isolated current sensing using AMC1301 for load current monitoring

- Isolated driver ISO5852S with reinforced isolation for driving High voltage SiC MOSFET and UCC5320S for driving middle Si IGBT