To do something useful, a microcontroller (MCU) must be connected to other devices. This connection is made through input/output (I/O) pins. More times than not, these days pins are multifunctional and can connect to A/Ds, D/As, linear functions (such as op amps and comparators), voltage references, and more. So for the design engineer, protecting these I/Os against potentially damaging static charges and other similar threats is of high importance.

In establishing proper protection for an MCU, engineers are finding that characteristics they have depended on for years have suddenly become less effective and they are forced to revisit problems of the past. Why? Principally, as a result of market pressure to reduce the cost of their products, semiconductor manufacturers have combined a higher level of integration with continued shrinking of process geometry, making die sizes smaller. As a result, implementing the necessary transient immunity protection to prevent malfunction due to transients on power and signal lines has become increasingly difficult.

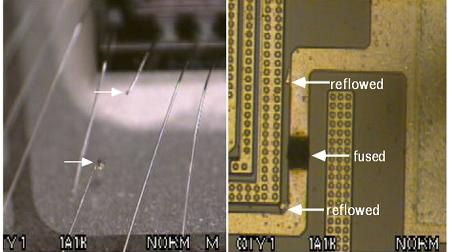

When geometries and IC feature sizes were larger, I/O pads had a lot of area for meaty drivers and good protection against ESD-induced damage. In the effort to improve yield, smaller die and pads are used, which, just by their nature, are less able to take a hit to protect a micro. As a rule of thumb, an electrostatic charge will always arc through the shortest possible path, and delicate micro I/O lines lead to more static discharge hits getting through.

This article looks at the different levels of MCU immunity to electrical fast transients (EFT), electrostatic discharge (ESD), and other events of short duration and suggests practical hardware and design techniques that can provide cost-effective ways of protecting microcontroller I/O lines. All parts, data sheets, tutorials, and development systems referenced here can be found online at Digi-Key’s website.

Immunity performance

One can categorize transient threats into three major types: electrostatic discharge (ESD), electrical fast transient (EFT), and surge transients. To ensure circuit robustness against these transients, the International Electrotechnical Commission (IEC) has specified a series of transient immunity tests in its IEC61000-4 family of electromagnetic compatibility (EMC) standards: IEC61000-4-2 covers ESD immunity (as applied to handheld devices, such as portable phones and computers), IEC61000-4-4 does the same for EFT immunity and IEC61000-4-5 handles surge immunity (lightning and industrial surges).

For more detail: Protecting MCU I/O Lines from ESD and Other Transients